1. Tujuan [KEMBALI]

1. memahami materi mengenai Shift Register Counter

2. membuat rangkaian simulasi Shift Register Counter2. Daftar Kompen [KEMBALI]

1. clock

clock

pada rangkaian digital berfungsi untuk mengalirkan data agar dapat

diproses oleh rangkaian.Tanpa

clock maka rangkaian digital (sekuensial) tidak akan bekerjaSemakin tinggi frekuensi clock maka rangkaian digital akan bekerja semakin cepat

2. J-K

FLIP-FLOP

Informasi yang disimpan dalam register ini dapat ditransfer dengan bantuan register geser . Shift Register adalah sekelompok sandal jepit yang digunakan untuk menyimpan banyak bit data. Bit yang disimpan dalam register tersebut dapat dibuat untuk bergerak di dalam register dan masuk / keluar dari register dengan menerapkan pulsa clock. Sebuah register geser n-bit dapat dibentuk dengan menghubungkan n flip-flop di mana setiap flip flop menyimpan sedikit data. Register yang akan menggeser bit ke kiri disebut "Shift left register". Register yang akan menggeser bit ke kanan disebut "Shift right register". Register geser pada dasarnya terdiri dari 4 jenis. Ini adalah:

1. Serial

In Serial Out register geser

2. Serial

In parallel Out shift register

3. Paralel

In Serial Out, register geser

4. Paralel

Dalam Paralel Keluar register geser

Serial-In Serial-Out Shift Register (SISO)

-

Register

geser, yang memungkinkan input serial (satu demi satu melalui jalur data

tunggal) dan menghasilkan output serial dikenal sebagai register shift

Serial-In Serial-Out. Karena hanya ada satu output, data meninggalkan

register geser satu per satu dalam pola serial, dengan demikian nama Serial-In

Serial-Out Shift Register.

Rangkaian

logika yang diberikan di bawah ini menunjukkan register geser keluar serial-in. Rangkaian

terdiri dari empat D flip-flop yang terhubung secara serial. Semua

flip-flop ini sinkron satu sama lain karena sinyal clock yang sama diterapkan

pada masing-masing flip flop.

Sirkuit di

atas adalah contoh register geser kanan, mengambil input data serial dari sisi

kiri flip flop. Penggunaan utama SISO adalah

untuk bertindak sebagai elemen penundaan.

Serial-In

Parallel-Out Register Register (SIPO) -

Register

geser, yang memungkinkan input serial (satu demi satu melalui jalur data

tunggal) dan menghasilkan output paralel dikenal sebagai register shift

Serial-In Parallel-Out.

Rangkaian

logika yang diberikan di bawah ini menunjukkan register geser

serial-in-parallel-out. Rangkaian terdiri dari empat D flip-flop yang

terhubung. Sinyal clear (CLR) terhubung di samping sinyal clock ke semua 4

flip flop untuk RESET. Output dari flip flop pertama terhubung ke input

flip flop berikutnya dan seterusnya. Semua flip-flop ini sinkron satu sama

lain karena sinyal clock yang sama diterapkan pada masing-masing flip flop.

Sirkuit di atas adalah contoh register geser kanan, mengambil input data serial dari sisi kiri flip flop dan menghasilkan output paralel. Mereka digunakan dalam jalur komunikasi di mana demultiplexing dari suatu garis data menjadi beberapa garis paralel diperlukan karena penggunaan utama register SIPO adalah untuk mengubah data serial menjadi data paralel.

Parallel-In

Serial-Out Shift Register (PISO) -

Register

geser, yang memungkinkan input paralel (data diberikan secara terpisah untuk

masing-masing flip flop dan secara simultan) dan menghasilkan output serial

dikenal sebagai register shift Parallel-In Serial-Out.

Rangkaian

logika yang diberikan di bawah ini menunjukkan register geser

paralel-dalam-serial-keluar. Rangkaian terdiri dari empat D flip-flop yang

terhubung. Input jam terhubung langsung ke semua flip flop tetapi data

input terhubung secara individual ke setiap flip flop melalui multiplexer pada

input setiap flip flop. Output dari flip flop sebelumnya dan input data

paralel dihubungkan ke input MUX dan output MUX terhubung ke flip flop

berikutnya. Semua flip-flop ini sinkron satu sama lain karena sinyal clock

yang sama diterapkan pada masing-masing flip flop.

Parallel-In

Parallel-Out Shift Register (PIPO) -

Register geser, yang

memungkinkan input paralel (data diberikan secara terpisah untuk masing-masing

flip flop dan secara simultan) dan juga menghasilkan output paralel yang

dikenal sebagai register shift Parallel-In parallel-Out.

Rangkaian logika yang diberikan

di bawah ini menunjukkan register geser paralel-paralel-keluar-keluar. Rangkaian terdiri dari empat D flip-flop yang terhubung. Sinyal (CLR) dan sinyal jam yang jelas terhubung ke semua 4 sandal

jepit. Dalam jenis register ini, tidak ada

interkoneksi antara flip-flop individual karena tidak diperlukan pengalihan

data secara berurutan. Data diberikan sebagai input

secara terpisah untuk setiap flip flop dan dengan cara yang sama, output juga

dikumpulkan secara individual dari masing-masing flip flop.

Register

geser Parallel in Parallel out (PIPO) digunakan sebagai perangkat penyimpanan

sementara dan seperti register SISO Shift, itu bertindak sebagai elemen

penundaan.

Daftar

Pergeseran Dua Arah -

Jika

kita menggeser angka biner ke kiri dengan satu posisi, itu sama dengan

mengalikan angka dengan 2 dan jika kita menggeser angka biner ke kanan dengan

satu posisi, itu sama dengan membagi angka dengan 2. Untuk melakukan operasi

ini kita membutuhkan register yang dapat menggeser data ke arah mana pun.

Register

pergeseran dua arah adalah register yang mampu menggeser data ke kanan atau

kiri tergantung pada mode yang dipilih. Jika mode yang dipilih adalah 1

(tinggi), data akan bergeser ke arah yang benar dan jika mode yang dipilih

adalah 0 (rendah), data akan bergeser ke arah kiri.

Rangkaian

logika yang diberikan di bawah ini menunjukkan register geser dua arah. Rangkaian

terdiri dari empat D flip-flop yang terhubung. Data input terhubung di dua

ujung sirkuit dan tergantung pada mode yang dipilih hanya satu dan gerbang

dalam keadaan aktif.

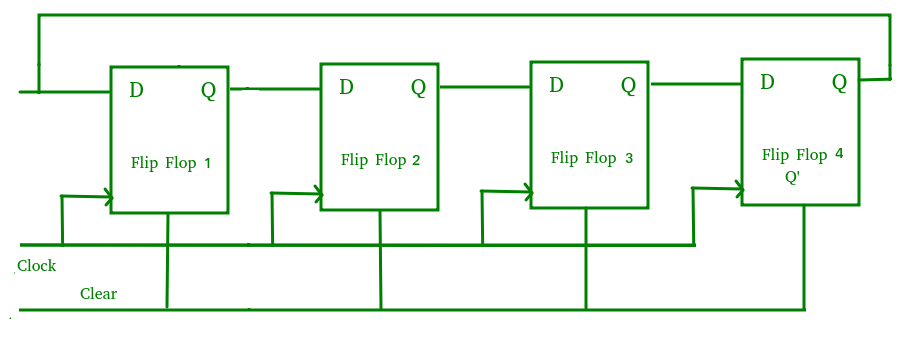

Ring Counter

Shift Register

5. Prinsip Kerja [KEMBALI]

Shift

Register Counters adalah register geser di mana output dihubungkan kembali ke

input untuk menghasilkan urutan tertentu. Ini pada dasarnya dari dua

jenis:

1. Penghitung

Dering -

Penghitung cincin pada dasarnya adalah

penghitung register geser di mana output dari flip flop pertama terhubung ke

flip flop berikutnya dan seterusnya dan output dari flip flop terakhir

diumpankan kembali ke input flip flop pertama, sehingga penghitung dering nama. Pola

data dalam register geser akan bersirkulasi selama pulsa clock diterapkan.

Rangkaian logika yang diberikan di bawah

ini menunjukkan Penghitung Cincin. Rangkaian terdiri dari empat D

flip-flop yang terhubung. Karena rangkaian terdiri dari empat sandal

jepit, pola data akan berulang setelah setiap empat jam pulsa seperti yang

ditunjukkan pada tabel kebenaran di bawah ini:

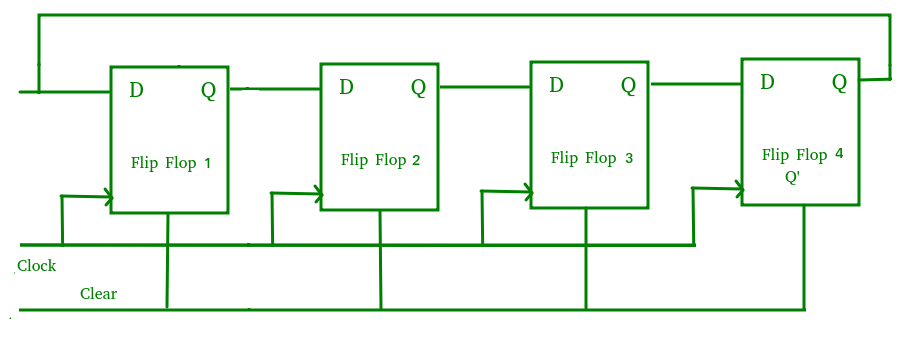

2. Johnson

Counter –

Sebuah

penghitung Johnson pada dasarnya adalah penghitung register geser di mana

output dari flip flop pertama terhubung ke flip flop berikutnya dan seterusnya

dan output terbalik dari flip flop terakhir diumpankan kembali ke input flip

flop pertama. Mereka juga dikenal sebagai counter ring bengkok.

Rangkaian

logika yang diberikan di bawah ini menunjukkan Counter Johnson. Rangkaian

terdiri dari empat D flip-flop yang terhubung. Penghitung Johnson tahap-n

menghasilkan urutan jumlah 2n keadaan yang berbeda, sehingga dikenal juga

sebagai penghitung mod-2n. Karena rangkaian terdiri dari empat sandal

jepit, pola data akan mengulangi setiap pulsa delapan jam seperti yang

ditunjukkan pada tabel kebenaran di bawah ini:

Keuntungan

utama dari penghitung Johnson adalah bahwa ia hanya membutuhkan n jumlah sandal

jepit dibandingkan dengan penghitung cincin untuk mengedarkan data yang

diberikan untuk menghasilkan urutan keadaan 2n.

6. Video Rangkain [KEMBALI]

Ring Counter

Shift Register

7. Link Download [KEMBALI]

- Video

- Rangkain

Tidak ada komentar:

Posting Komentar